“Faster†is a must-have for every system designer, as is FPGA-based design. If you often try to maximize the performance of each MHz from the FPGA design, then you will definitely be interested in a white paper that Xilinx just released. Its topic is "Enabling High-Speed ​​Radio Designs with Xilinx All Programmable FPGAs and SoCs". If you are designing a high-speed radio cellular system, you should look at this. A white paper. But the guides and techniques are much more than just wireless design. It's also suitable for high-speed systems designed with programmable logic.

The purpose of the white paper is that "if you meet some simple design principles, high-speed wireless design can be easily built on the 7-series FPGA architecture. Xilinx has created a design example of a typical wireless data path, indicating a medium-speed (-2) Almost 100% of the slice resources used on the device support clock frequencies above 500 MHz.

However, the content in this white paper applies to all data path designs.

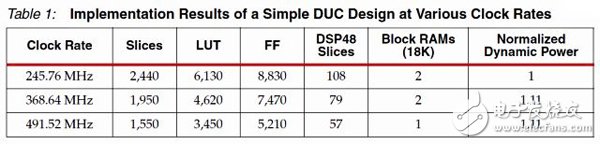

The example architecture in the white paper is a single antenna path DUC (Digital Upconverter) architecture that supports three different clock rates: 245.76 MHz, 368.64 MHz, and 491.52 MHz. The design is built using IP (FIR compiler), structural components (eg, instantiation of DSP48 primitives), interface VHDL code, etc. in the Xilinx System Generator tool. The white paper shows the key utilization metrics that the DUC design implements at three clock rates:

The first thing to note is that the DSP48 slice count is generally inversely proportional to the clock rate. Block RAM resources also decrease with clock rate according to the step function. This is more common in radio signal processing designs, where block RAM is basically used to store a large set of coefficients for functional operations at relatively high sampling rates, such as the sine/cosine values ​​of DDS (Direct Digital Synthesizer), peak cancellation pulse generation. CFR (Crest Factor Attenuation) factor in the device, or nonlinear function sampling in the DPD (Digital Predistortion) model.

This analysis is not as simple as a logical resource. When the clock frequency is converted from 368.64 to 491.52 MHz (1.33 clock ratio), the data amount by proportional LUT and FF is reduced by 1.34 and 1.44 times, respectively. The clock rate is doubled from 245.76 to 491.52 MHz, which is reduced by 1.8 times and 1.7 times. This non-linear behavior is basically to perform signal processing control logic without linear amplification at the clock frequency.

The signal sampling rate also affects resource utilization. For example, a filter bandwidth with a sampling rate of 25 Msamples/sec is slightly less than twice the logic required to run at a bandwidth of 500 MHz at 250 MHz. The multiphase implementation bandwidth with a sampling rate of 500 Msamples/sec doubles the required logic resources at 250 MHz operation compared to 500 MHz bandwidth. The first-order estimate of the use of logic resources is that an increase in the clock frequency by a factor of x corresponds to a 0.85 to 1.1-fold reduction in logic utilization.

These design data, together with more data in the white paper, show common recommendations for designing FPGA-based, high-performance systems:

Proper pipeline programming is of course a key factor in designing high-speed programs.

When you need to build more than one block RAM storage, you can optimize the configuration by minimizing data reuse and resource utilization. For example, 16K memory that stores 16-bit data is best built using 16K &TImes; 1-bit block RAM instead of 1K &TImes; 16-bit block RAM.

DSP slice logic essentially supports higher clock rates. The number of logic levels and data routing paths limits speed, so a register should be inserted at each or both LUT levels when building a high speed design.

Define a reasonable hierarchy and divide the design into corresponding functional modules according to logical partitions. This hierarchy provides a way to facilitate the registration of output at hierarchical boundaries, thereby limiting the critical path of a particular module. This makes it easy to analyze and fix the timing paths that are located in a single module. In fact, when positioning ultra-high clock speeds, multiple register levels should be used at some level of the hierarchy to optimize timing and leave more design space for the back-end tools. A good design hierarchy should integrate the relevant logic to make area grouping and logical compression more efficient.

Establish an appropriate hierarchy to get repeatable results across multiple modules.

Implementing properties at the module level makes the code simple and extensible, and it propagates all the signals declared in the module.

Good clock management and clock distribution methods are critical.

Minimize the number of independent master clocks.

Place clock components on top of the design hierarchy to share clocks across multiple modules, which reduces the clock resources required, improves timing performance, and reduces resource and power utilization.

Use appropriate resynchronization techniques between unrelated clock domains.

Again, you must define enough reset strategies. In general, you do not need to reset each register. Resetting registers does not require creating high fanout nets because it reduces timing performance and increases routing complexity. Reset only when the reset is absolutely necessary.

Minimize the size of the reset network.

Avoid global resets.

A synchronous reset is preferred, which is actually mandatory for the DSP48 slice and the block RAM.

Limit the use of the clock "enable". In fact, this rule is difficult to implement because the clock "enable" in a multi-cycle implementation usually requires evaluation of data samples or operator outputs. Achieving effective power reduction techniques is very effective. In any case, the clock enable signal must be properly registered to remove high fanout nets.

So if you're developing a high-speed FPGA-based design, even if it's not a digital RF application, you'll need to download and read the white paper as soon as possible to get your design done - "High-speed radio design with Xilinx All Programmable FPGAs and SoCs."

Ferrite Permanent Magnets C8,Black Ferrite Magnet y10t,y35 Ferrite Rotor Magnet,Permanent Ferrite Magnet C5

HU NAN YUBANG MAGNETIC MATERIAL CO.,LTD , https://www.ybmagnet.com