When designing an FPGA-based electronic system, it is generally necessary to use an external test device such as an oscilloscope or a logic analyzer to test the input and output signals, and send the signal to the test device for observation and analysis by means of the test probe. Of course, the premise is that you need to keep enough pins so that you can select the signal to drive the I/O for testing. However, external test equipment often encounters such a situation when testing an FPGA system: the number of I/O pins of the FPGA is not rich enough, and the PCB layout and package complexity make the I/O pins difficult to lead, and the external test probes have an influence. The possibility of FPGA signal timing and integrity.

If you can embed a logic test module with external test device functions inside the FPGA, then the above problems can be solved one by one. SignalTapII is such an embedded logicana Iyzer, referred to as SignalTapII ELA. It is an internal logic analysis software integrated in the Quartus II software. It can be used to observe internal signal waveforms in real time, making it easy for users to find design flaws.

1 Principle of SignalTapII ELA

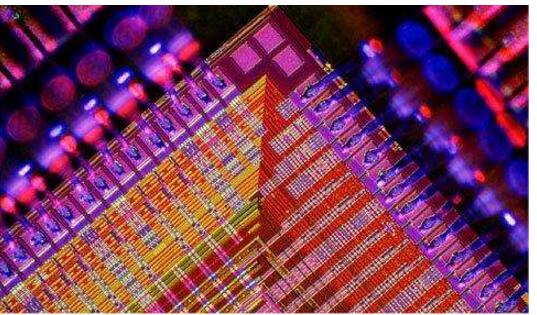

SignalTapII ELA is the second generation system level debugging tool in Quartus software. The SignalTapII ELA code and the system logic code are combined and compiled by Quartus II, integrated, place and route, the generated sol file contains SignalTapII ELA, and the sof file is configured into the FPGA. When the FPGA is running, once the trigger condition of the signal to be tested is met, the SignalTapII ELA starts immediately, captures the signal data to be tested according to the frequency of the sampling clock and temporarily stores it in the RAM in the FPGA chip. The sampled data continuously refreshes the on-chip memory and finally passes. The JTAG port transfers the captured signal from the on-chip RAM to the Quartus II real-time display. The principle flow of SignalTapII ELA is shown in Figure 1.

In actual engineering, adding SignalTapII ELA will not affect the original logic function of the system.

2 SignalTapII ELA configuration

The basic configuration process of SignalTapII ELA is as follows:

1 Add a sampling clock. SignalTaplI ELA samples on the rising edge of the clock. Any signal in the design system can be used as the sampling clock. According to Altera's recommendation, it is best to use the synchronous system global clock as the sampling clock. However, in practical applications, most use separate sampling clocks, which can sample slow signals in the system under test, or signals related to the working clock. Of course, the frequency of the sampling clock is greater than the highest frequency of the signal under test, otherwise the waveform of the signal under test will have a large error.

2 Define the sampling depth. The sampling depth determines the size of the sample storage of the signal to be tested, and the depth that can be sampled is determined according to the remaining RAM block capacity in the design and the number of signals to be tested. If there are more signals to be tested, the sampling depth is shallower in the case of the same number of I/O banks. The increase or decrease of the number of signals to be tested and the depth of the sampling depth will directly change the occupancy of the RAM block, and the sampling depth ranges from 0 to 128 KB.

3 Define the RAM type. Set which RAM block resources are occupied in the chip. As the sampling depth changes, the data lines and address line widths of the RAM block can be divided into various combinations. For example, the sampling depth is 1 KB, and the RAM data line and address line can be divided into 2 & TImes; 512 or 4 & TImes; 256 and other combinations. So on and so forth.

4 Define the trigger position. Pre trigger posiTIon indicates that 12% of the sampled data is before the trigger and 88% is the trigger; Center trigger posiTIon indicates that the sampled data is half before and after the trigger; Post trigger position indicates that the sampled data is 88% before the trigger, and 12% is After the trigger.

5 Trigger condition level setting. SignalTapII ELA supports multi-trigger-level triggering, supporting up to 10 levels of triggering, helping to filter out irrelevant data and find the data you need faster. If there are multiple levels of triggering conditions, first analyze the first level of triggering conditions. If the first level is TRUE, then it is analyzed whether the second level is satisfied, and the clock sampling data is finally triggered until all trigger conditions are TRUE.

6 trigger conditions. Set a binding trigger condition. The independent trigger condition Basic of a single signal can be allowed to directly adopt a signal inside a single external or design module; or a combination of multiple node signals can be triggered to trigger the condition Advanced, which constitutes a trigger condition equation of the trigger function. For example, the enable signal ENA is triggered with the 4-bit output signal Q and the trigger condition = ENA&(Q=15).

Sky Curtain Uno,Landscape Lighting Of Outdoor Buildings,Ip67 Led Cabinet Light,Led Light Aluminum Alloy

Kindwin Technology (H.K.) Limited , https://www.ktlleds.com