Many industrial systems need to measure critical parameters with the highest accuracy. Examples include seismic monitoring, energy exploration, gas flu testing, and silicon wafer manufacturing. In each case, these systems extend the boundaries of cutting-edge signal processing technology and require ppm accuracy. The design of such systems is highly sophisticated and incorporates wide dynamic range sensors, high-order control loops, and the highest performance integrated circuit components.

The core of many precision industrial systems is an analog-to-digital converter (ADC). The ADC plays a vital role in transforming analog signals into digital signals for digital signal processing. The accuracy and performance of the ADC often determine the accuracy and performance of the overall system. This article will discuss how breakthrough data conversion performance can achieve higher accuracy and lower cost for next-generation industrial systems.

Precision industrial systems require a high resolution ADC to digitize the actual analog signal. Analog signal links, including ADCs and supporting signal conditioning circuits (such as amplifiers, filters, and references), typically require excellent DC specifications such as offset, gain, and linearity.

To achieve ppm-level resolution and accuracy, many precision industrial systems implement digital calibration to eliminate any system-level offset and gain errors. As a result, system accuracy is often limited by errors that cannot be suppressed with occasional calibration, and system designers may be more concerned with the potential drift of important parameters than their static values. For example, a precision system may not only require ppm-level accuracy at a fixed temperature, but also require drift accuracy below ppm/°C over a wide operating temperature range.

The linearity of the ADC is of the utmost concern for overall system accuracy. The linearity of the ADC is determined by the complex interaction between the analog input signal and the internal design and architecture of the ADC. ADC nonlinearity errors are extremely difficult to calibrate at the system level because such errors vary widely between digital codes and because they can be a strong function of temperature. The linearity and stability of the ADC over the entire temperature range is extremely important for the overall accuracy of a precision system.

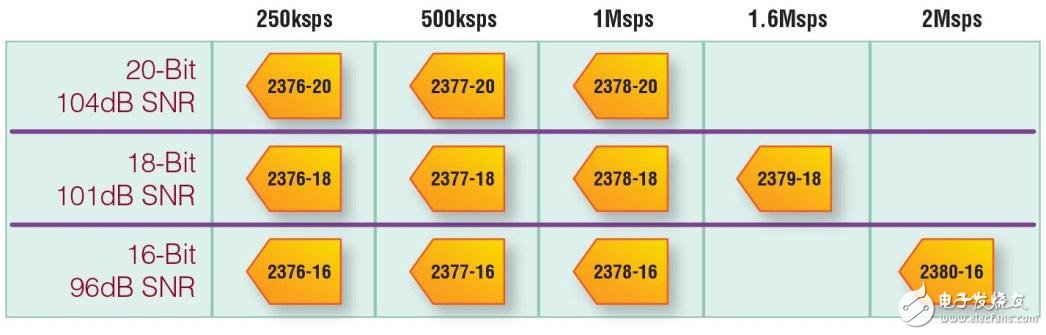

To address these design challenges, a new 20-bit SAR ADC family offers unprecedented levels of performance and accuracy, simplifying the design of high-precision industrial systems. The LTC2378-20 is the flagship of a family of pin and software compatible SAR ADCs with up to 20 bits of lossless code resolution and up to 104dB signal-to-noise ratio (SNR) with sample rates ranging from 250ksps to 2Msps. The DC accuracy of the LTC2378-20 is particularly impressive: the ADC integral nonlinearity (INL) error is typically less than 0.5ppm and is guaranteed to be less than 2ppm over the entire operating temperature range (-40°C to +85°C) (for all codes) ). The maximum offset error is 13ppm (with 0.007ppm/°C drift) and the gain error is 10ppm (with 0.05ppm/°C drift). This exceptional level of performance is achieved at very low operating power consumption from 5.3mW (at 250ksps) to 21mW (at 1Msps). Each device is available in a small MSOP-16 package and a DFN-16 package. Figure 1 summarizes this new ADC family.

Figure 1: Complete 20 / 18 / 16-bit pin-compatible SAR ADC family

SAR ADC characteristicsA SAR ADC is characterized by its ability to acquire accurate snapshots while simulating an input signal and to perform an analog-to-digital conversion operation within a single clock cycle. SAR ADCs are known for performing asynchronous "start and run" operations, and they are easy to use due to the ability to immediately get conversion results in the same clock cycle. The ability to produce accurate conversion results without cycle delays, even after a long idle period, makes SAR ADCs ideal for a wide range of precision applications, including sensors, control loops, data acquisition and automated testing. equipment. Other types of ADCs (for example, ΔΣ ADCs and pipelined ADCs) require multiple clock cycles to complete a single conversion.

Circuit architecture The LTC2378-20 with ppm level guaranteed linearity and accuracy is a disruptive product for many precision industrial systems. The LTC2378-20 is designed with a proprietary architecture that ensures linearity and minimizes sensitivity to changes in temperature and other operating conditions. As a result, an unprecedented 2ppm INL specification is guaranteed over the entire operating temperature range.

The SAR ADC algorithm is based on the binary search principle. The analog input is sampled into a capacitor and sequentially compared to a fraction of the reference voltage selected using the SAR algorithm. The SAR ADC consists of three key components: a capacitor-based digital-to-analog converter (CDAC), a fast low-noise comparator circuit, and a successive approximation register. The INL performance of traditional SAR ADCs may be limited by the limited matching accuracy of individual capacitors in CDAC, and many high precision SAR ADCs use analog or digital trimming methods to improve matching accuracy. However, when temperature changes and package and board stress are applied, the CDAC capacitor matching accuracy will always decrease and it is possible to limit the linearity of the ADC.

By leveraging a proprietary architecture that makes INL unaffected by CDAC capacitor mismatch, the LTC2378-20 achieves its state-of-the-art INL performance, giving it the kind of presence in harsh industrial environments. Excellent robustness due to temperature variations and package stress effects. In addition, the comparator circuit has been carefully designed to balance speed, power, and noise specifications, ultimately enabling the LTC2378-20 to achieve an unprecedented 104dB signal-to-noise ratio (SNR) and power consumption of only 21mW (at 1Msps), and No cycle delay was introduced. The power consumption of the LTC2378-20 in the SAR ADC family is proportional to the sample rate, so when they operate at 1ksps, the power consumption is only microwatts.

The level of accuracy achieved by the LTC2378-20 was previously only available through the use of much slower ADC architectures such as ΔΣ ADCs or multi-slope ADCs. High channel count automated test equipment often uses this slow ADC architecture to perform high precision DC measurements and utilizes multiplexers to enable a single meter to serve multiple inputs. The ADC conversion time is typically adjusted over a wide range to sacrifice speed to increase resolution. However, when the sampling rate is higher than 100ksps, the measurement resolution is often limited to less than 16 bits. The LTC2378-20 can take millions of readings per second with a noise resolution of 2.3ppm (standard deviation of noise, 104dB SNR). The results of multiple readings of the same analog signal can be combined digitally to improve noise resolution and produce performance beyond multi-slope ADCs. For example, by averaging 10 sample blocks, the LTC2378-20 actually operates at 1Msps/10 = 100ksps and has a noise resolution of 0.7ppm (114dB SNR).

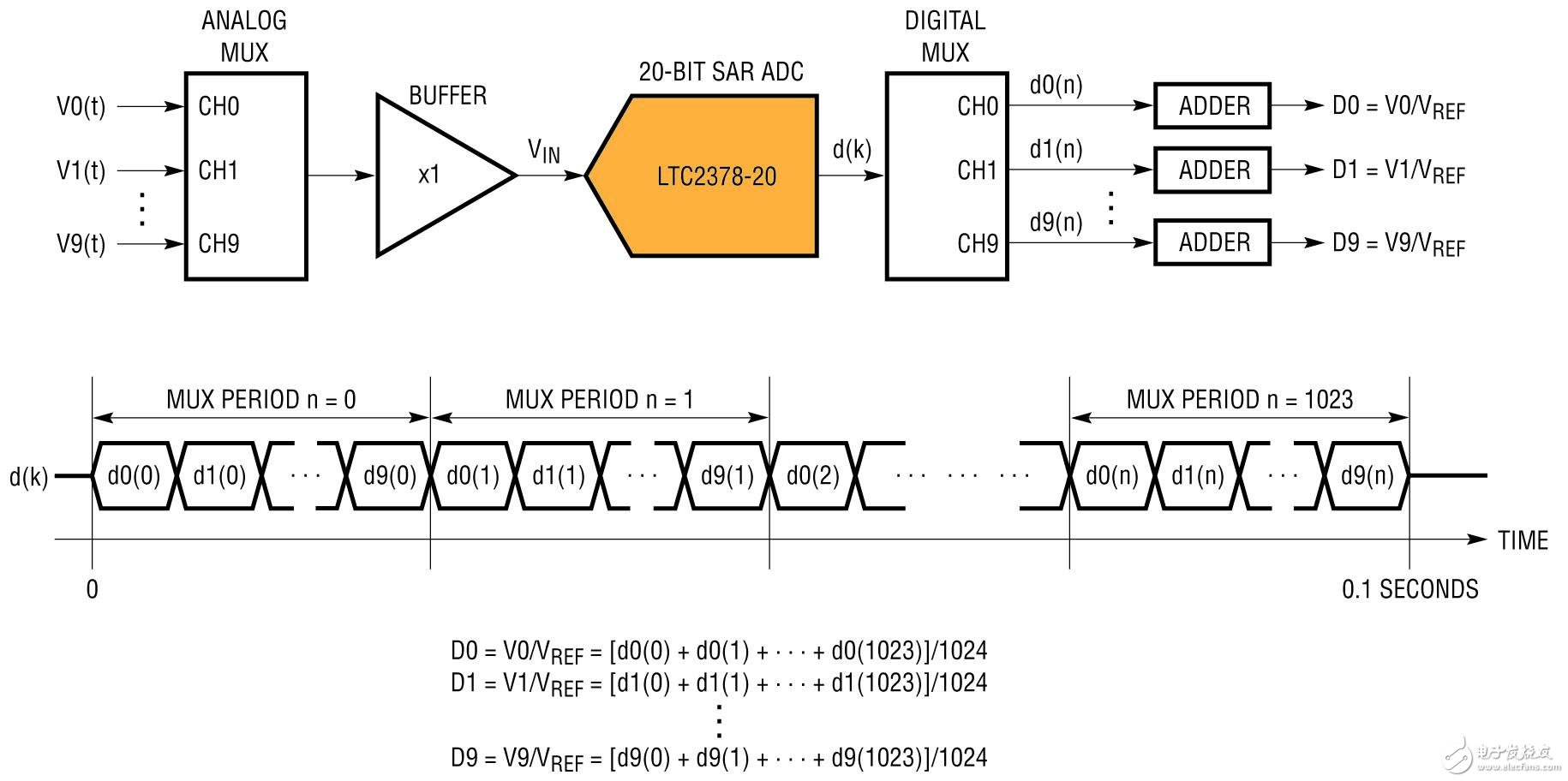

The ΔΣ ADC and multi-slope ADC can be configured to average an analog input signal during an observation/integration cycle to suppress noise and interference. A 100ms observation period is typically used to simultaneously reject 50Hz and 60Hz line frequency interference, resulting in a throughput rate of only 10sps. Accordingly, when using a multi-slope ADC, it will take a full second to serve 10 multiplexed channels. Figure 2 shows a single LTC2378-20 ADC operating at 102.4ksps sampling rate with a multiplexing circuit to simultaneously measure all 10 signals (interleaved) over a 100ms observation period. While maintaining the line frequency interference suppression corresponding to the 100ms observation period, the throughput rate is increased, and the multiple is the number of multiplexing channels (here, 10 times, but can be higher), thereby greatly improving the automatic test equipment. Productivity. In this example, noise resolution is increased by averaging 1024 samples taken from each channel during the observation period and provides 22-bit noise resolution (0.07ppm or 70nVrms). The averaging operation can be done with a simple adder (which can be easily implemented with programmable logic or a processor). As a result, the LTC2378-20 significantly increases measurement speed while maintaining the important advantages of previous architectures.

Figure 2: The LTC2378-20 is configured to simultaneously read and average 10 analog inputs over a 100ms observation period.

Longkou Libo Insulating Material Co.,Ltd. , https://www.liboinsulation.com